Figure 11.57

1. Pendahuluan[kembali]

Rangkaian counter merupakan salah satu rangkaian penting dalam sistem digital yang berfungsi untuk menghitung pulsa clock secara berurutan dan menampilkan hasilnya dalam bentuk urutan biner. Counter banyak digunakan dalam aplikasi seperti penghitung, pembagi frekuensi, dan sistem kendali digital. Pada praktikum ini, akan dibahas sebuah rangkaian counter 3-bit yang dibangun menggunakan tiga buah flip-flop JK, di mana setiap flip-flop mewakili satu bit dari hasil hitungan. Analisis terhadap urutan keluaran (count sequence) dan sifat self-starting dari rangkaian ini sangat penting untuk memastikan keandalan counter dalam aplikasi nyata.

2. Tujuan [kembali]

- Menganalisis dan memahami urutan kerja dari three-bit counter yang dibentuk dengan flip-flop.

- Menentukan apakah counter bersifat self-starting.

- Mengimplementasikan rangkaian berdasarkan diagram logika yang diberikan.

- Mengamati urutan keluaran logika dari rangkaian counter saat diberi pulsa clock.

3. Alat dan Bahan [kembali]

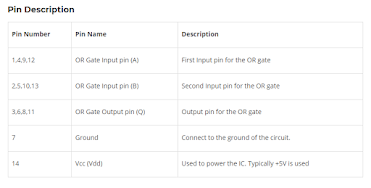

a. Gerbang OR

OR adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0. Apabila semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila salah satu, sebagian, atau seluruhnya berlogika 1.

IC 74LS73 adalah dual JK flip-flop tipe negatif-edge triggered dengan clear (reset) asynchronous aktif rendah. Artinya:

- IC ini berisi 2 buah JK flip-flop.

- Output flip-flop akan berubah hanya saat tepi turun (falling edge) dari sinyal clock.

- Ketika J = K = 1, maka flip-flop akan toggle (berubah ke keadaan berlawanan).

- Pin Clear dapat digunakan untuk mengatur ulang output ke 0 tanpa menunggu clock.

Fungsi utama: digunakan untuk menyimpan 1 bit data, membentuk counter, register, pembagi frekuensi, dll.

Gerbang NOT atau disebut rangkaian inventer (pembalik). Tugas rangkaian NOT (pembalik) ialah memberikan suatu keluaran yang berbanding terbalik dengan masukan.

AND adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila salah satu, sebagian atau semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila semua inputnya berlogika 1. Adapun simbol beberapa tipe gerbang AND seperti gambar :

Clock adalah sinyal pulsa periodik yang digunakan sebagai pemicu (trigger) dalam rangkaian sekuensial seperti flip-flop. Sinyal clock mengatur kapan suatu elemen logika seperti flip-flop dapat mengubah output-nya. Clock biasanya berupa gelombang persegi dengan frekuensi tertentu, dan dapat dibuat dari sumber eksternal seperti osilator atau komponen pulse generator di simulasi.

4. Dasar Teori [kembali]

Counter digital adalah rangkaian sekuensial yang terdiri dari beberapa flip-flop yang terhubung sedemikian rupa sehingga dapat menghitung jumlah pulsa clock yang masuk. Salah satu jenis flip-flop yang sering digunakan dalam pembuatan counter adalah flip-flop JK, karena kemampuannya untuk toggle (berubah keadaan) ketika kedua input J dan K bernilai logika tinggi. Pada counter biner, setiap flip-flop merepresentasikan satu bit hasil hitungan dan output dari satu flip-flop dapat digunakan sebagai input clock untuk flip-flop berikutnya (ripple counter).

Flip-Flop JK adalah elemen penyimpan dasar yang digunakan dalam counter karena kemampuannya untuk toggle (berubah kondisi) saat J = K = 1. Dalam rangkaian ini:

Output dari satu flip-flop digunakan sebagai masukan ke flip-flop lainnya.

Gerbang logika (AND, NOT) digunakan untuk mengontrol kapan flip-flop akan berubah kondisi.

Konsep self-starting pada counter mengacu pada kemampuan rangkaian untuk kembali ke urutan hitungan yang benar secara otomatis, meskipun secara tidak sengaja berada pada kondisi yang tidak diinginkan (undesired state). Counter yang tidak self-starting dapat berhenti atau berputar pada kondisi yang salah jika terjadi gangguan, sehingga keandalan sistem menurun. Self-starting counter berarti jika rangkaian secara tidak sengaja berada di kondisi tidak valid (seperti 000, 100, atau 101 dalam konteks soal), maka rangkaian akan otomatis kembali ke urutan yang benar hanya dengan memberikan pulsa clock, tanpa intervensi eksternal.

Example

- Contoh 1:

Sebuah counter asinkron 3-bit menggunakan flip-flop JK menerima sinyal clock dengan frekuensi 8 kHz. Hitung frekuensi output pada flip-flop ketiga (MSB).

Jawaban:

Setiap flip-flop membagi frekuensi clock menjadi setengahnya.

Flip-flop pertama output: 8 kHz / 2 = 4 kHz

Flip-flop kedua output: 4 kHz / 2 = 2 kHz

Flip-flop ketiga output: 2 kHz / 2 = 1 kHz

Jadi, frekuensi output pada flip-flop ketiga adalah 1 kHz. - Contoh 2:

Jika counter asinkron 3-bit mulai dari keadaan 000, berapa urutan hitungan biner yang dihasilkan setelah menerima 5 pulsa clock?

Jawaban:

Urutan hitungan biner: 0 (000), 1 (001), 2 (010), 3 (011), 4 (100), 5 (101)

Setelah 5 pulsa clock, output counter adalah 101.

- Problem 1:

Mengapa counter asinkron 3-bit disebut juga ripple counter dan apa kelemahan utamanya?

Jawaban:

Counter asinkron disebut ripple counter karena pulsa clock "mengalir" atau "bergelombang" dari flip-flop pertama ke flip-flop berikutnya secara berantai. Kelemahannya adalah delay propagasi yang menyebabkan output tidak berubah secara serentak, sehingga dapat menimbulkan ketidakakuratan pada frekuensi tinggi. - Problem 2:

Bagaimana cara membuat counter MOD-6 menggunakan counter asinkron 3-bit?

Jawaban:

Counter MOD-6 menghitung dari 0 sampai 5, lalu reset ke 0. Pada counter 3-bit, kondisi 6 (110) dan seterusnya harus di-reset. Dengan menambahkan gerbang logika (misalnya NAND) yang mendeteksi kondisi 110 dan mengirim sinyal reset ke flip-flop, counter dapat di-reset saat mencapai hitungan 6, sehingga menghasilkan MOD-6.

- Soal 1:

Apa fungsi utama dari counter asinkron 3-bit?

a. Mengubah sinyal analog menjadi digital

b. Menghitung jumlah pulsa clock secara berurutan

c. Menyimpan data secara permanen

d. Menghasilkan sinyal clock baru

e. Mengalihkan jalur sinyal - Soal 2:

Pada counter asinkron 3-bit, berapa jumlah keadaan berbeda yang dapat dihitung sebelum kembali ke nol?

a. 4

b. 6

c. 7

d. 8

e. 16

(Karena 3 bit menghasilkan 2^3 = 8 keadaan)

5. Percobaan [kembali]

a) Prosedur[kembali]

Siapkan komponen di simulator (Proteus atau Multisim):

3 buah JK Flip-Flop (IC 74LS73)

1 buah gerbang AND dan 1 buah NOT

Sumber clock (pulser) dan tombol reset (jika diperlukan)

LED atau probe untuk memantau output A, B, dan C

Rancang koneksi flip-flop:

Hubungkan semua flip-flop ke clock bersama

Hubungkan input J dan K dari FF-A ke logika 1 (toggle selalu)

Hubungkan input J dan K dari FF-B ke output Q dari A

Hubungkan input J dan K dari FF-C ke hasil gerbang AND antara A dan B

Tambahkan output LED/probe pada masing-masing Q dari flip-flop A, B, dan C untuk memantau keadaan.

Jalankan simulasi dan amati urutan keluaran setiap kali clock aktif.

Catat apakah semua 8 kombinasi 3-bit (000 hingga 111) muncul. Jika tidak, analisis apakah counter bisa kembali dari kondisi tidak valid ke urutan valid tanpa reset manual.

b) Rangkaian Simulasi dan Prinsip Kerja [kembali]

Prinsip Kerja :

Rangkaian pada gambar terdiri dari tiga flip-flop JK yang masing-masing diberi label sebagai flip-flop C, B, dan A, yang mewakili bit C (LSB), B, dan A (MSB) dari output counter. Setiap flip-flop dikonfigurasi dengan input J dan K yang dihubungkan ke kombinasi output flip-flop lain, sehingga membentuk urutan hitungan tertentu.

- Flip-flop C: J dan K dihubungkan ke logika 1, sehingga selalu toggle pada setiap pulsa clock.

- Flip-flop B: J dan K dihubungkan ke output C, sehingga hanya toggle ketika C bernilai 1.

- Flip-flop A: J dan K dihubungkan ke output B, sehingga hanya toggle ketika B bernilai 1.

Namun, dari analisis pada soal, diketahui bahwa rangkaian ini tidak self-starting. Jika counter secara tidak sengaja masuk ke salah satu kondisi yang tidak diinginkan (seperti 101, 110, atau 111), maka counter tidak akan kembali ke urutan yang benar secara otomatis, sehingga diperlukan reset manual atau modifikasi rangkaian agar menjadi self-starting.

c) Video Simulasi [kembali]

6. Download File [kembali]

- Download Rangkaian disini

- Download Video Rangkaian

- Download Datasheet And Gate klik disini

- Download Datasheet Or Gate klik disini

- Download Datasheet Nor Gate klik disini

- Download HTML disini

Komentar

Posting Komentar