CHAPTER 8 : Figure 8.28, 8.29, 8.30

1. Pendahuluan[kembali]

Multiplexer merupakan salah satu rangkaian logika digital yang berfungsi untuk memilih salah satu dari beberapa sinyal input dan meneruskannya ke satu output. Rangkaian ini bekerja berdasarkan sinyal kontrol atau select line yang menentukan input mana yang aktif. Multiplexer banyak digunakan dalam sistem komunikasi, pengolahan data, dan rangkaian kontrol karena mampu menyederhanakan pengaturan jalur data dan meningkatkan efisiensi transmisi informasi.

Decoder adalah rangkaian logika digital yang berfungsi mengubah sinyal input biner menjadi keluaran unik pada salah satu dari banyak jalur output. Setiap kombinasi input biner akan mengaktifkan hanya satu output, sementara output lainnya tetap tidak aktif. Decoder banyak digunakan dalam sistem digital seperti pemilihan memori, tampilan digital, dan rangkaian kontrol, karena mampu mengonversi kode biner menjadi sinyal yang mudah diidentifikasi dalam aplikasi praktis.

Full Subtractor adalah rangkaian logika digital yang berfungsi melakukan operasi pengurangan antara dua bit biner, dengan mempertimbangkan pinjaman (borrow) dari tahap sebelumnya. Rangkaian ini memiliki tiga input, yaitu minuend, subtrahend, dan borrow-in, serta menghasilkan dua output, yaitu selisih (difference) dan borrow-out. Full Subtractor banyak digunakan dalam sistem aritmetika digital, seperti rangkaian pengurang biner, kalkulator elektronik, dan unit aritmetika komputer.

2. Tujuan [kembali]

- Memahami cara kerja multiplexer (MUX) dalam membentuk fungsi logika.

- Menganalisis fungsi logika yang dihasilkan dari susunan beberapa buah MUX.

- Mempelajari cara menyusun rangkaian kombinasi menggunakan multiplexer 2-to-1 dan 8-to-1

- Mempelajari konsep kerja full subtractor dalam logika digital.

- Mengimplementasikan fungsi full subtractor menggunakan 3-to-8 decoder dan gerbang NOR.

- Menganalisis hasil keluaran berupa selisih (Difference) dan pinjaman (Borrow Out) berdasarkan input biner.

3. Alat dan Bahan [kembali]

a) Multiplexer

Multiplexer adalah suatu perangkat yang dapat menerima beberapa input data dan hanya satu diantara input yang akan dilewat ke output pada suatu waktu.

b) Decoder

Decoder adalah suatu perangkat yang dapat mengubah suatu sistem bilangan biner yang terdapat pada bagian input, menjadi sistem bilangan yang lain pada outputnya.

M1 adalah Jumlah ouput decoder yang lebih rendah

M2 adalah Jumlah ouput decoder yang lebih tinggi

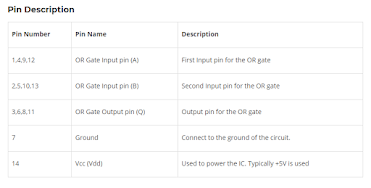

Gerbang OR adalah salah satu rangkaian logika dasar dalam elektronika digital yang berfungsi menghasilkan output bernilai logika 1 (HIGH) jika salah satu atau lebih inputnya bernilai logika 1.

-

Jika semua input = 0 → output = 0

-

Jika ada minimal satu input = 1 → output = 1

Gerbang AND ini memerlukan dua atau lebih input untuk menghasilkan satu output. Jika semua atau salah satu inputnya merupakan bilangan biner 0, maka outputnya akan menjadi 0. Sedangkan jika semua input adalah bilangan biner 1, maka outputnya akan menjadi 1.

IC 7411 berisi tiga gerbang AND dengan tiga input dari keluarga Transistor Transistor Logic

Konfiugurasi pin:

- Vcc : Kaki 14

- GND : Kaki 7

- Input : Kaki 1, 2, 3, 4, 5, 9,10,11 dan 13

- Output : Kaki 6, 8, dan 12

e) Inverter (NOT)

Jenis berikutnya adalah gerbang NOT. Gerbang NOT ini berfungsi sebagai pembalik keadaan. Jika input bernilai 1 maka outputnya akan bernilai 0 dan begitu juga sebaliknya.

Logic state adalah kondisi atau level sinyal dalam rangkaian digital yang menunjukkan nilai logika tertentu, biasanya berupa logika tinggi (1) atau logika rendah (0). Logic state ini merepresentasikan informasi digital yang diproses oleh perangkat elektronik, seperti komputer atau mikrokontroler. Selain dua kondisi dasar tersebut, dalam beberapa sistem juga bisa terdapat kondisi tidak pasti seperti high impedance (Z) atau undefined, yang menunjukkan bahwa sinyal tidak aktif atau sedang mengambang. Pemahaman tentang logic state penting untuk desain, analisis, dan troubleshooting rangkaian digital.

Logic probe adalah alat elektronik yang digunakan untuk mendeteksi dan menampilkan status logika (HIGH atau LOW) dari sinyal digital pada suatu rangkaian. Alat ini sangat berguna dalam perbaikan, pengujian, dan analisis rangkaian digital, karena memberikan informasi instan mengenai keadaan logika dari sebuah titik pengujian.

4. Dasar Teori [kembali]

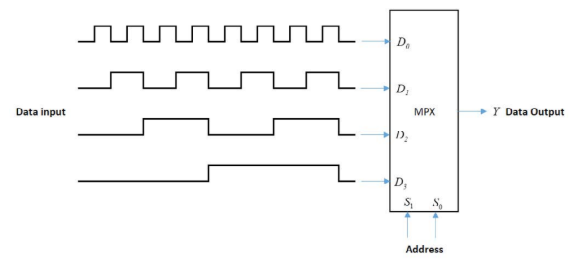

Multiplexer, atau sering disingkat MUX, adalah rangkaian logika digital yang berfungsi sebagai penyeleksi data, yaitu memilih salah satu dari beberapa input data untuk diteruskan ke satu jalur output. Jumlah input multiplexer biasanya merupakan pangkat dua, misalnya 2, 4, 8, 16, dan seterusnya. Pemilihan input dilakukan oleh sinyal kendali yang disebut select line. Sebagai contoh, multiplexer 4-to-1 memiliki 4 jalur input, 2 bit select line, dan 1 output. Kombinasi bit pada select line menentukan input mana yang dihubungkan ke output. Multiplexer banyak digunakan untuk efisiensi pengiriman data, sistem komunikasi, rangkaian kontrol, serta meminimalkan jumlah jalur kabel pada sistem digital.

Prinsip kerja multiplexer adalah dengan mengambil bit-data dari setiap sinyal masukan secara bergantian dan mengirimkannya ke sinyal keluaran. Multiplexer juga sangat berguna dalam komunikasi data, karena memungkinkan data yang berasal dari beberapa sumber berbeda untuk dikirim melalui jalur yang sama. Dalam praktiknya, multiplexer digunakan dalam berbagai aplikasi seperti pemrosesan sinyal, pemrosesan gambar, dan komunikasi data. Contoh sederhana penggunaan multiplexer adalah pada sistem audio yang menggunakan beberapa mikrofon. Dalam hal ini, multiplexer akan memilih sinyal audio dari setiap mikrofon secara bergantian dan mengirimkannya ke sinyal keluaran tunggal. Secara teknis, multiplexer terdiri dari beberapa komponen seperti sumber masukan, pemilih masukan, dan pengendali. Sumber masukan adalah sinyal-sinyal masukan yang akan digabungkan, sedangkan pemilih masukan adalah komponen yang bertugas memilih sinyal masukan yang akan dikirimkan ke keluaran.

Decoder merupakan rangkaian logika digital yang berfungsi mengubah kode biner pada input menjadi keluaran unik pada salah satu dari beberapa jalur output. Decoder biasanya memiliki jumlah output sebesar 2ⁿ jika jumlah inputnya n-bit. Misalnya, decoder 3-to-8 memiliki 3 input biner dan 8 output, di mana hanya satu output yang aktif untuk setiap kombinasi input. Fungsi utama decoder adalah memecah sinyal biner menjadi sinyal terpisah yang dapat mengontrol bagian tertentu dari sistem, seperti memilih chip memori (memory addressing), mengontrol tampilan digital (seperti seven segment), atau digunakan dalam rangkaian kontrol logika. Decoder juga dapat digabungkan secara cascading untuk menghasilkan lebih banyak jalur output sesuai kebutuhan sistem.

Dekoder n-ke-2n dan m gerbang OR eksternal dapat digunakan untuk mengimplementasikan kombinasi rangkaian dengan n input dan m output. Misal pada penerapan empat variabel Fungsi Boolean dengan 12 minterms menggunakan dekoder baris 4-ke-16 dan gerbang OR eksternal. OR gerbang di sini harus menjadi gerbang 12-input. Dalam semua kasus seperti itu, di mana jumlah minterm dalam suatu Fungsi Boolean dengan n variabel lebih besar dari 2n /2 (atau 2n-1 ), fungsi komplementer Boolean akan memiliki lebih sedikit minterm. Dalam hal ini akan lebih baik menggunakan NORing daripada ORing dengan output fungsi boolean.

Full Subtractor adalah rangkaian logika digital yang digunakan untuk melakukan pengurangan dua bit biner dengan mempertimbangkan adanya pinjaman (borrow) dari tahap pengurangan sebelumnya.

Inputnya ada tiga:

- Minuend (A) → angka yang dikurang.

- Subtrahend (B) → angka pengurang.

- Borrow-in (Bin) → pinjaman dari pengurangan bit sebelumnya.

Outputnya ada dua:

- Difference (D) → hasil selisih pengurangan.

- Borrow-out (Bout) → pinjaman ke tahap pengurangan berikutnya.

Prinsip kerja Full Subtractor adalah mengurangkan bit A dengan bit B dan juga memperhitungkan borrow-in. Jika nilai A lebih kecil dari B ditambah borrow-in, maka rangkaian akan menghasilkan borrow-out yang menunjukkan bahwa pinjaman harus dilakukan dari bit yang lebih tinggi. Full Subtractor biasanya dibangun dengan menggabungkan dua Half Subtractor dan sebuah gerbang OR untuk menghasilkan borrow-out.

Secara logika, output Difference dapat dihitung dengan persamaan

|

| Tabel Kebenaran full subtractor |

1. Determine the function performed by the combinational circuit of Fig. 8.29. (4-to-1 Multiplexer)

Rangkaian pada Gambar 8.29 membentuk MUX 4-to-1 menggunakan tiga MUX 2-to-1.

Fungsinya:

F=I0 jika S1S0=00

F=I1 jika S1S0=01

F=I2 jika S1S0=10

F=I3 jika S1S0=11

Jadi, output F adalah hasil dari MUX 4-to-1.

- Difference (selisih): Output 1, 2, 4, 7

- Borrow Out (pinjam): Output 3, 5, 6, 7

1. Sebuah 4-to-1 multiplexer memiliki input I0, I1, I2, dan I3, serta dua bit select line S1 dan S0. Diketahui nilai input sebagai berikut:

-

I0 = 0

-

I1 = 1

-

I2 = 0

-

I3 = 1

Jika nilai select line S1 S0 = 11, tentukan nilai output multiplexer.

Penyelesaian :

- Multiplexer 4-to-1 akan memilih salah satu input sesuai nilai S1 S0.

- S1 S0 = 11 → desimal = 3 → memilih input I3.

- Nilai I3 = 1.

-

A = 0

-

B = 1

-

Borrow-in (Bin) = 1

Tentukan Difference (D) dan Borrow-out (Bout) yang dihasilkan!

Penyelesaian :

Rumus difference (D):

Substitusi:

Rumus borrow-out (Bout):

Hitung:

-

(karena A = 0)

-

-

-

Sehingga:

(Dalam logika OR, 1+1+1 tetap 1.)

Jadi, Difference = 0 dan Bout = 1

1. Sebuah 8-to-1 multiplexer memiliki 3 bit select line (S2, S1, S0). Jika input yang terhubung ke I5 = 1 dan semua input lain = 0, maka nilai output multiplexer saat S2 S1 S0 = 101 adalah

A. 0

B. 1

C. Error

D. Tidak dapat ditentukan

2. Sebuah full subtractor memiliki input A = 1, B = 0, dan Borrow-in (Bin) = 1. Berapakah nilai Difference (D) yang dihasilkan?

A. 0

B. 1

C. Error

D. Tidak dapat ditentukan

5. Percobaan [kembali]

a) Prosedur[kembali]

- Buka aplikasi proteus

- Pilih komponen yang dibutuhkan, pada rangkaian ini dibutukan gerbang XOR, Gerbang AND, dan gerbang OR.

- Rangkai setiap komponen menjadi rangkaian yang diinginkan

- Ubah spesifikasi komponen sesuai kebutuhan

- Jalankan simulasi rangkaian.

b) Rangkaian Simulasi dan Prinsip Kerja [kembali]

- Fig 8.28

- Fig 8.29

MUX1 dan MUX2 masing-masing menerima dua input data:

MUX1 memilih antara I₀ dan I₁ berdasarkan selektor S₀

MUX2 memilih antara I₂ dan I₃ berdasarkan selektor S₀

Output dari MUX1 dan MUX2 kemudian menjadi input bagi MUX3.

MUX3 memilih salah satu output dari MUX1 atau MUX2 berdasarkan selektor S₁

Fungsi ini merupakan fungsi logika dari 4-to-1 multiplexer.

- Fig 8.30

Rangkaian menggunakan decoder 3-to-8 untuk mendekode kombinasi input A, B, dan Bin menjadi salah satu dari delapan output (D0–D7). Setiap output decoder mewakili satu kondisi dari input A, B, Bin. Kemudian, output-output tertentu dari decoder digabungkan menggunakan gerbang OR untuk menghasilkan nilai Difference dan Borrow berdasarkan tabel kebenaran.

Selanjutnya, output dari gerbang OR dibalik menggunakan gerbang NOT (NOR secara fungsional), karena full subtractor dalam gambar ini menggunakan NOR untuk meminimalkan penggunaan komponen (NOR sebagai universal gate).

c) Video Simulasi [kembali]

6. Download File [kembali]

- Rangkaian 8.28 klik disini

- Rangkaian 8.29 klik disini

- Rangkaian 8.30 klik disini

- Download Datasheet And Gate klik disini

- Download Datasheet Or Gate klik disini

- Download Datasheet Nor Gate klik disini

- Download Datasheet IC 74LS283 klik disini

- Download Datasheet Decoder (IC7447) klik disini

Komentar

Posting Komentar