Figure 11.31

1. Pendahuluan[kembali]

Rangkaian pencacah (counter) merupakan salah satu aplikasi utama dari flip-flop dalam sistem digital. Counter digunakan untuk menghitung pulsa clock yang masuk dan menghasilkan urutan biner yang sesuai dengan desain. Pada contoh ini, Figure 11.31 menunjukkan implementasi perangkat keras dari counter menggunakan 3 buah JK Flip-Flop serta gerbang logika untuk mengatur eksitasi flip-flop berdasarkan kondisi saat ini (present state). Rangkaian ini adalah bentuk nyata dari analisis tabel keadaan dan transisi dari contoh 11.9, yang bertujuan untuk memproduksi urutan bit tertentu berdasarkan logika input.

2. Tujuan [kembali]

- Mempelajari cara kerja dan implementasi counter berbasis flip-flop JK.

- Mengimplementasikan tabel keadaan menjadi rangkaian fisik dengan logika eksitasi yang sesuai.

- Memahami hubungan antara present state, next state, dan input eksitasi JK.

- Melatih keterampilan dalam menyusun dan menguji rangkaian logika sekuensial di simulator.

3. Alat dan Bahan [kembali]

- IC ini berisi 2 buah JK flip-flop.

- Output flip-flop akan berubah hanya saat tepi turun (falling edge) dari sinyal clock.

- Ketika J = K = 1, maka flip-flop akan toggle (berubah ke keadaan berlawanan).

- Pin Clear dapat digunakan untuk mengatur ulang output ke 0 tanpa menunggu clock.

Fungsi utama: digunakan untuk menyimpan 1 bit data, membentuk counter, register, pembagi frekuensi, dll.

4. Dasar Teori [kembali]

Counter dapat dibedakan menjadi dua jenis utama, yaitu asynchronous counter (ripple counter) dan synchronous counter. Pada asynchronous counter, pulsa clock hanya diberikan pada flip-flop pertama, dan output flip-flop tersebut menjadi clock bagi flip-flop berikutnya, sehingga terjadi delay propagasi. Sedangkan pada synchronous counter, semua flip-flop menerima pulsa clock secara bersamaan, sehingga perubahan output terjadi serentak dan lebih cepat.

Counter digunakan dalam berbagai aplikasi seperti penghitung waktu (timer), pembagi frekuensi, penghitung kejadian, odometer, dan sistem digital lainnya yang membutuhkan pencacahan pulsa secara otomatis. Modulus (MOD) counter menunjukkan jumlah keadaan berbeda yang dapat dicapai counter sebelum kembali ke keadaan awal. Misalnya, MOD-8 counter menghitung dari 0 sampai 7 secara berulang.

Counter adalah rangkaian logika sekuensial yang menghitung banyaknya pulsa clock dan menghasilkan keluaran dalam bentuk biner. Rangkaian counter dibangun dari beberapa flip-flop JK, karena jenis ini fleksibel dalam menentukan kondisi eksitasi untuk berbagai jenis transisi.

Flip-Flop JK memiliki karakteristik:

Jika J = K = 1 → output akan toggle

Jika J = 0, K = 1 → output reset

Jika J = 1, K = 0 → output set

Jika J = K = 0 → tidak ada perubahan

Tabel kebenaran dari counter (seperti yang ditampilkan dalam Tabel 11.13) menunjukkan transisi antar keadaan dan input yang dibutuhkan untuk mencapai transisi tersebut. Dengan menggunakan peta Karnaugh atau analisis eksitasi flip-flop, kita bisa menyusun logika yang mengatur J dan K berdasarkan output saat ini dari flip-flop lainnya.

- Contoh 1:

Sebuah ripple counter 4-bit menerima sinyal clock dengan frekuensi 10 kHz. Berapa frekuensi output pada flip-flop ke-4?

Jawaban:

Setiap flip-flop membagi frekuensi clock menjadi setengahnya. Jadi, pada flip-flop pertama frekuensi output adalah 5 kHz, flip-flop kedua 2,5 kHz, flip-flop ketiga 1,25 kHz, dan flip-flop keempat 0,625 kHz. - Contoh 2:

Sebuah counter MOD-8 dibuat menggunakan 3 flip-flop. Jika input clock diberikan pulsa terus menerus, berapa hitungan maksimal yang dapat dicapai sebelum counter kembali ke nol?

Jawaban:

MOD-8 berarti counter menghitung dari 0 sampai 7, jadi maksimal hitungan adalah 8 keadaan sebelum reset ke nol.

- Problem 1:

Jelaskan perbedaan utama antara asynchronous (ripple) counter dan synchronous counter!

Jawaban:

Asynchronous counter memberikan clock hanya pada flip-flop pertama, sedangkan flip-flop berikutnya menerima clock dari output flip-flop sebelumnya, menyebabkan delay propagasi. Synchronous counter memberikan clock secara bersamaan ke semua flip-flop, sehingga perubahan output terjadi serentak dan lebih cepat. - Problem 2:

Apa yang dimaksud dengan counter modulo N dan bagaimana menentukan jumlah flip-flop yang dibutuhkan untuk counter tersebut?

Jawaban:

Counter modulo N adalah counter yang menghitung sampai N-1 dan kemudian kembali ke nol. Jumlah flip-flop yang dibutuhkan adalah minimal n sehingga 2^n ≥ N, dimana n adalah jumlah bit (flip-flop) yang diperlukan.

- Soal 1:

Counter yang memberikan output secara serentak pada semua flip-flop disebut:

a. Asynchronous counter

b. Synchronous counter

c. Ripple counter

d. Decade counter

e. Frequency divider - Soal 2:

Berapa jumlah flip-flop minimum yang dibutuhkan untuk membuat counter MOD-16?

a. 2

b. 3

c. 4

d. 8

e. 16

5. Percobaan [kembali]

a) Prosedur[kembali]

Siapkan komponen dalam simulator (Proteus atau lainnya):

3 buah JK Flip-Flop (IC 7476 atau 74LS73)

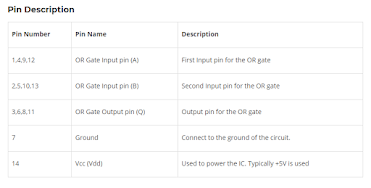

Gerbang logika AND dan OR (IC 7408 dan 7432)

Sumber clock (pulser atau gelombang persegi)

Probe atau LED untuk memantau output flip-flop A, B, dan C

Buat koneksi clock secara paralel ke semua flip-flop (sinkron).

Hubungkan output flip-flop ke gerbang logika sesuai dengan rangkaian pada Gambar 11.31, yang menghasilkan sinyal J dan K masing-masing flip-flop berdasarkan present state.

Hubungkan output gerbang logika ke input J dan K pada flip-flop terkait.

Tambahkan LED atau probe pada output flip-flop untuk memantau keadaan logika (Q) dari A, B, dan C.

Jalankan simulasi dan amati perubahan keadaan dari output Q pada setiap pulsa clock.

Cocokkan hasil simulasi dengan tabel keadaan yang diberikan (Tabel 11.13) untuk memverifikasi bahwa counter bekerja dengan benar.

b) Rangkaian Simulasi dan Prinsip Kerja [kembali]

Prinsip Kerja

Rangkaian ini terdiri dari 3 flip-flop JK (FF-A, FF-B, FF-C) yang diatur secara sinkron, karena ketiganya berbagi clock yang sama. Namun, perubahan kondisi masing-masing flip-flop hanya terjadi jika input J dan K-nya memenuhi syarat yang telah ditentukan dari tabel keadaan.

Output dari flip-flop digunakan sebagai masukan ke rangkaian logika (AND, OR) untuk menentukan input J dan K pada flip-flop lainnya.

Dengan konfigurasi gerbang logika tersebut, flip-flop akan toggle atau berubah sesuai dengan yang diatur dalam tabel transisi.

Ini menghasilkan urutan logika biner tertentu saat clock diberikan, misalnya mod-6 counter atau urutan biner yang tidak berurutan.

Rangkaian ini adalah implementasi langsung dari tabel transisi berdasarkan kondisi sebelumnya (present state) dan kondisi selanjutnya (next state), sehingga kita bisa melihat realisasi praktis dari teori eksitasi flip-flop JK.

c) Video Simulasi [kembali]

6. Download File [kembali]

- Download Rangkaian disini

- Download Datasheet And Gate klik disini

- Download Datasheet Or Gate klik disini

- Download Datasheet Nor Gate klik disini

- Download HTML disini

Komentar

Posting Komentar